What UpTickPro can do for you?

Build. Test. Iterate

Processor and SoC Verification, Redefined

Make your RISC-V designs rock solid with test suites, checkers, and coverage collectors. Python-powered CoCoTb Environments and AI-driven VIPs handle everything—from UARTs to custom accelerators.

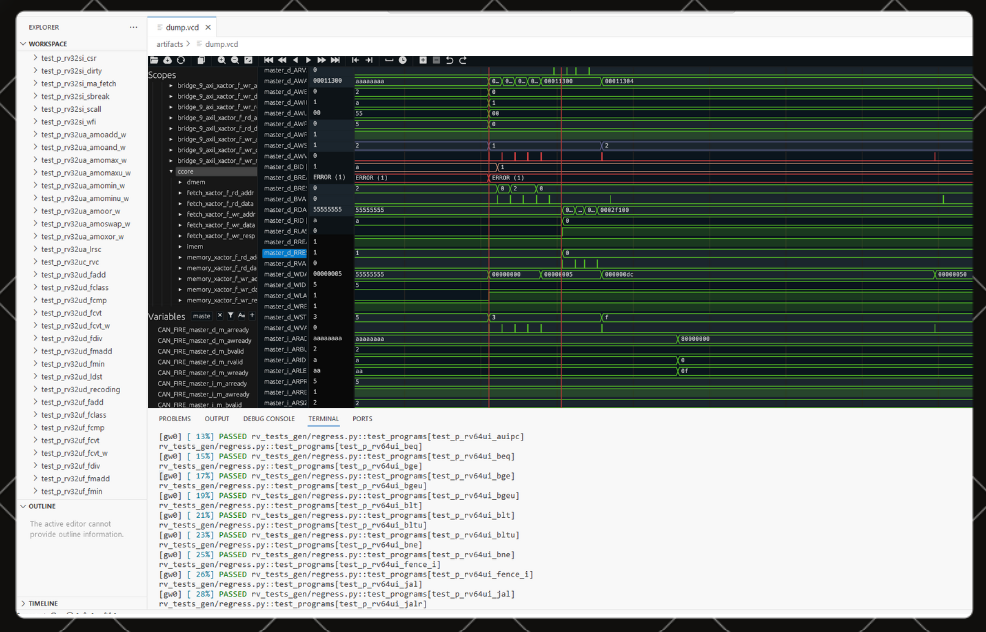

Emulation with Enhanced Debug

Speed up development and debugging with a FireSim-based FPGA prototyping platform. Designed for rapid prototyping and efficient issue resolution, it keeps you moving fast.

Software Bringup from Day One

Develop and deploy with ease using Debian on QEMU. Built for smooth RISC-V application development, it gets you up and running from day one.

Choose Your Plan

Enterprise

Designed for large teams needing custom solutions

- Custom Users

- Custom IDEs

- Access to RISC-V and Peripheral VIPs

- CoCoTb Env

- Debug & Coverage viewers

- DevOps support

- AI assisted testing and debug

Paid Add-Ons

- On-prem support

- Sofware Bringup IDE

- Fully supported Emulation IDE

Frequently Asked Questions

-

What is UpTickPro?

UpTickPro is a platform that provides RISC-V verification, emulation and software solutions. We deliver ready-to-deploy environments that can be used for verifying a RISC-V design, prototyping on FPGA or developing the software stack.

-

How can we get started in using the platform?

Please connect with us either by filling out the form (prefered) or contacting us through email: info@vyomasystems.com. We will get you started on using the platform.

-

I am not sure of using it in the cloud, is there any other option?

Yes, we provide both on-prem and cloud solutions. Feel free to contact us to know how to use them.

-

Can we customize the environment? We need to add few of our tools in the mix!

Yes, absolutely. We can customize the development environment as well as the ops fitting your needs.

They Trust Us

Email:

info@vyomasystems.com

Address:

D Block, 4th Floor, Module 403, IIT Madras Research Park, Kanagam Rd, Kanagam, Tharamani, Chennai, Tamil Nadu 600113